inter<sub>s</sub>il

## PSPICE Performs Op Amp Open Loop Stability Analysis (HA5112)

Application Note

November 1996

AN9536.1

The open loop stability plot of an op amp circuit, which is commonly called a Bode [1] plot, is often difficult to observe in the lab because most op amps saturate when the loop is opened. Since most op amps have a very high open loop gain, one must work with very small signals when attempting to measure the open loop transfer function, so even if an answer is obtained it usually contains a large error. When PSPICE is employed for the open loop analysis an identical saturation problem occurs because the PSPICE model is built to emulate all of the op amp characteristics. The PSPICE saturation will manifest itself in either of two ways: the program will not be able to calculate a DC bias point or the results of any calculations will be in error.

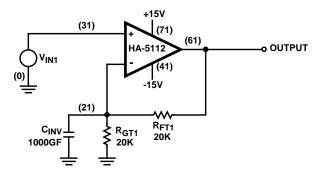

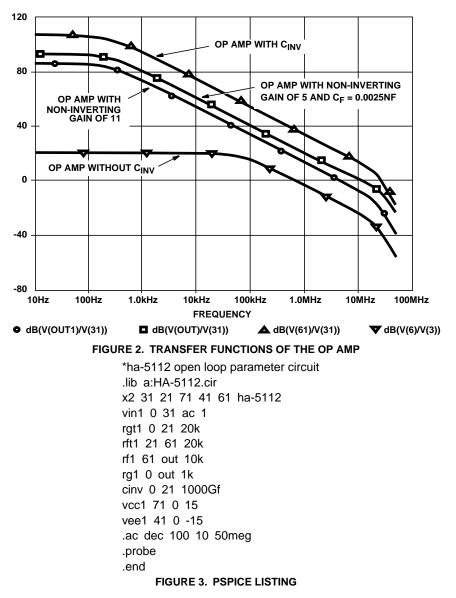

A method of obtaining an accurate open loop PSPICE plot of an op amp is to fool the circuit as shown in Figure 1A. The capacitor, CINV, is added from the inverting node to ground where it acts like an AC short for the feedback signal. There is still DC feedback, so the program will converge to a DC bias point. The plot will show the op amp open loop gain characteristics if the AC output of PSPICE is configured to be a dB plot of the ratio of the output to input voltage. Although the phase characteristic can be plotted by PSPICE, it is simpler to approximate it from the gain plot by noting where the slope changes (the -3dB breakpoints), and assuming a 45 degree phase shift resulted from the slope change. Several open loop plots are shown in Figure 2. The curve marked with inverted triangles is for the op amp circuit with no feedback resistance (RFT1 and CINV omitted), and it has no relation to the open loop op amp curve shown in the HA-5112 Data Sheet [2] because PSPICE did not calculate the correct bias point. This illustrates the problems that occur when the circuit DC feedback path is broken in an attempt to plot the open loop transfer function. The curve marked with the non-inverted triangles is for the op amp with RFT1 included and CINV connected from the inverting node to ground. Notice that the resulting curve closely approximates the open loop curve shown in the HA-5112 Data Sheet. Also, note that the slope changes to -40dB/decade (called a -2 slope) before the curve passes through 0dB, so the op amp will probably oscillate if it is connected in a gain of one configuration.

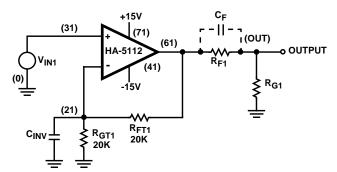

Because  $C_{INV}$  grounds the inverting node for AC,  $R_{FT1}$  appears as a small load to the op amp and has negliable effect on the AC performance. The output of the op amp shown in Figure 1A is the op amp open loop transfer function, so when  $R_{F1}$  and  $R_{G1}$  are added as shown in Figure 1B, the circuit calculates the open loop stability equation  $A\beta = A(R_{G1})/(R_{F1}+R_{G1})$ .

FIGURE 1A. CIRCUIT FOR DETERMINING THE OP AMP OPEN LOOP TRANSFER FUNCTION

## FIGURE 1B. STABILITY ANALYSIS MODEL DESCRIBED IN THE PSPICE LISTING

The curve marked with the diamonds is for  $R_{F1} = 10K$  and  $R_{G1} = 1K$ . The closed loop non-inverting gain would be 11, thus it should be stable according to the data sheet. Notice that the slope is -1 when it passes through 0dB so the closed loop circuit will be stable. The curve marked with the squares is for a closed loop non-inverting gain of 5 with a feedback capacitor,  $C_F$ , added in parallel with RF1. Without  $C_F$  the circuit is marginally stable at best because the op amp open loop transfer function (see Figure 2) has a gain of about 9dB when the slope changes from -1 to -2, and the attenuation per the stability equation is -13.9dB.  $C_F$  was added to the circuit to introduce a zero into the open loop transfer function, and the zero cancels out the pole at the second breakpoint causing the curve to pass through 0dB with a -1 slope. Thus,  $C_F$  stabilizes the circuit for a closed loop gain of 5.

This analysis does not account for manufacturing tolerances which can be as large as 2 to 1. There are two factors to keep in mind when considering manufacturing tolerances, and they are the 0dB frequency intercept tolerance and the open loop gain intercept tolerance.

The gain intercept has a tolerance of  $\pm$ 6dB, or a factor of two. The gain of the op amp is proportional to gmR<sub>H</sub> where gm is the input transconductance and R<sub>H</sub> is the effective impedance seen by gm. The first pole frequency is proportional to 1/R<sub>H</sub>C, so the gain bandwidth is constant with respect to variations in R<sub>H</sub>. This means that if the gain intercept has increased by 6dB the first pole frequency has

moved in by an octave, or conversely, if the gain intercept has decreased by 6dB the first pole has moved out by an octave. The constant gain bandwidth criteria tends to keep the 0dB intercept constant for a given gain intercept change, but there is enough movement to bear watching.

The value of the op amp's internal compensation capacitor might have a  $\pm 15\%$  tolerance, and the value of this capacitor determines the 0dB frequency intercept. When this tolerance is added to the gmR<sub>H</sub> error the tolerance may be as much as  $\pm 30\%$ . The curve for the op amp open loop gain has a 27MHz 0dB frequency intercept, so a prudent design must be able to function with any 0dB frequency intercept from 19MHz to 35MHz.

Op amp stability can be modeled quite well with SPICE, and it often obtains excellent stability results, but it is not prudent to neglect the testing. If the closed loop circuit is driven by a step function, the peak of the overshoot [3] is an excellent indicator of the phase margin or stability.

## References

- Bode, H.W., Network Analysis and Feedback Amplifier Design, D. Van Nostrand, Inc., 1945.

- [2] Intersil Corporation, Linear and Telecom ICs for Analog Signal Processing Applications, 1993-94.

- [3] Mancini, R.A., Feedback, Op Amps and Compensation, Intersil Corporation, Application Note 9415.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 guality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com